台积电3DFabric技术助力楷登电子实现高性能先进封装IP流片

【本站】6月9日消息,楷登电子(Cadence)日前宣布在台积电3纳米(N3E)工艺技术基础上成功流片其最新的Cadence 16G UCIe 2.5D先进封装IP。这款IP采用了台积电的3DFabric CoWoS-S硅中介层技术,能够提供超高的带宽密度、高效的低功耗性能以及卓越的低延迟,非常适合需要极高算力的应用场景。

Cadence的UCIe IP为裸片到裸片通信提供了开放标准,随着人工智能/机器学习(AI/ML)、移动、汽车、存储和网络应用推动从单片集成向系统级封装(SiP)Chiplet的转变,裸片到裸片通信变得越来越重要。目前,Cadence正在与许多客户合作,其中包括使用N3E工艺的UCIe先进封装IP的测试芯片已经开始发货并可供使用。这个预先验证的解决方案可以实现快速集成,为客户节省时间和精力。

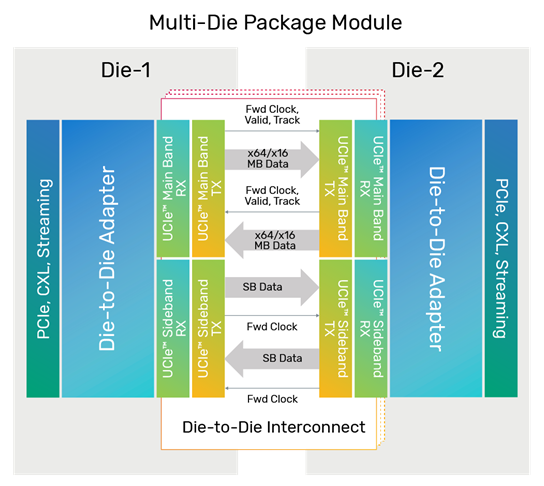

Cadence的UCIe PHY和控制器的异构集成简化了Chiplet解决方案,并具有裸片可重复使用性。完整的解决方案包括UCIe先进封装PHY、UCIe标准封装PHY和UCIe控制器等。UCIe先进封装PHY专为支持5Tbps/mm以上Die边缘带宽密度而设计,能够在显著提高能效的同时实现更高的吞吐量性能,并可以灵活集成到多种类型的2.5D先进封装中。UCIe标准封装PHY则可以帮助客户降低成本,同时保持高带宽和高能效。而UCIe控制器则是一种软IP核,可以在多个技术节点进行综合,并支持多种选项,如流、PCI Express(PCIe)和CXL协议。

据本站了解,UCIe联盟主席Debendra Das Sharma博士表示:“UCIe联盟支持各公司设计用于标准和先进封装的Chiplet。我们非常高兴地祝贺Cadence在实现先进封装测试芯片的流片里程碑上取得的成就,该芯片使用基于UCIe 1.0规范的die-to-die互连。成员公司在IP(扩展)和VIP(测试)方面的进展是该生态系统中的重要组成部分。再加上UCIe工作组的成果,业界将继续看到基于开放行业标准的新Chiplet设计进入市场,促进互操作性、兼容性和创新。”

Cadence一直是Chiplet系统解决方案产品领域的先驱,并将继续推动先进节点和封装架构中各种多Chiplet应用的性能和能效极限。Cadence的全球副总裁兼IP事业部总经理Sanjive Agarwala表示:“我们认为,协调整个行业的互连标准十分重要,而UCIe IP可作为桥梁,为大型系统级芯片提供开放式Chiplet解决方案,达到或超过制造的最大光罩极限。基于台积电N3E工艺的UCIe先进封装流片是为客户提供开放式Chiplet连接标准的关键里程碑和承诺。”

Cadence 16G UCIe 2.5D先进封装IP支持Cadence的智能系统设计(Intelligent System Design™)战略,该战略旨在实现SoC的卓越设计。

相关文章

- 音画完美融合!三星电视神经元量子点处理器带来立体环绕声场

- 中国游戏公司米哈游:《原神》推动营收翻倍,创造全球收入超410亿美元

- 汽车芯片领域迎来三星电子与现代汽车的历史性合作

- 消息曝光:三星计划提高NAND存储晶圆价格

- 三星Galaxy S23系列:环保创新 回收海洋塑料保护蓝色家园

- 中国电信移动用户数突破40000万户 5G用户达28723万户

- 广汽集团1-5月累计销量达92.7万辆 新能源车型同比增长112.21%

- 专家建议亚马逊重新审视战略:剥离非核心业务 专注创新

- 全球裁员计划后 英国电信集团首席执行官薪酬冻结

- 三六零实际控制人周鸿祎完成股权转让 胡欢持有约4.47亿股份

- 波音787“梦想客机”遭遇质量问题频发

- 台积电考虑调整代工价格应对市场压力

- 百度智能云文心千帆大模型平台开放“文心一言-Turbo”测试申请

- 中国科学院与腾讯合作开发基于人工智能的心理咨询系统,获得专利授权

- 华为副总裁甘斌:中国5G千兆网建设取得巨大成就

- 中国空间站成功与天舟五号货运飞船再次对接

热门教程

Win11每次开机会检查tpm吗?Win11每次开机是否会检查tpm详情介绍

2Win11正式版怎么安装安卓APK应用?Win11安装安卓APK文件方法

3系统之家装机大师怎么用?系统之家装机大师使用教程

4Win10 21H1更新KB5003637后任务栏不能在底部显示怎么办?

5Win11电脑下载的文件被自动删除怎么办?

6Win11资源管理器的样式如何切换?Win11资源管理器样式切换方法

7Win11蓝屏怎么修复?win11蓝屏修复教程

8老电脑怎么装win11系统?老电脑一键升级Win11系统教程

9Win11正式版如何固定“此电脑”到任务栏?

10Win10和Win11哪个好用?Win10和Win11区别介绍

装机必备 更多+

重装教程

大家都在看

电脑教程专题 更多+