台积电第二代 3nm 工艺到来,N3E 芯片已流片

10 月 26 日消息,Alphawave 公司表示,其已经流片(Tape out)了业界首批使用台积电 N3E 制造技术(第二代 3 纳米级工艺节点)的芯片之一。该芯片已由台积电生产,并成功通过了所有必要的测试,将于本周晚些时候在台积电的 OIP 论坛上展示。

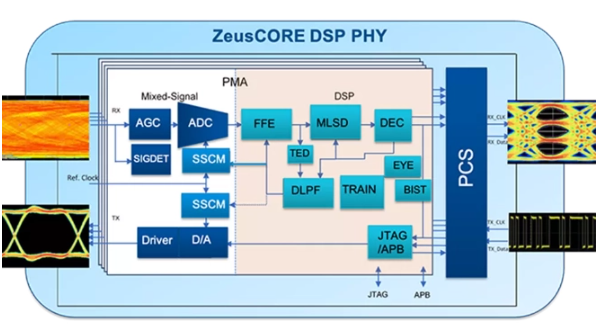

该芯片是 Alphawave IP ZeusCORE100 1-112Gbps NRZ / PAM4 串行器-解串器(SerDes),支持未来几年将流行的众多标准,包括 800G 以太网、OIF 112G-CEI、PCIe 6.0 和 CXL3.0。据称,SerDes 支持超长的通道,为下一代服务器提供灵活的连接解决方案。

Alphawave IP

Alphawave 公司总裁兼首席执行官 Tony Pialis 称:“Alphawave 很荣幸成为首批利用台积电最先进的 3 纳米技术的公司之一。我们的合作关系将继续带来创新的高速连接技术,为最先进的数据中心提供动力,我们很高兴能在台积电 OIP 论坛活动中展示这些解决方案。”

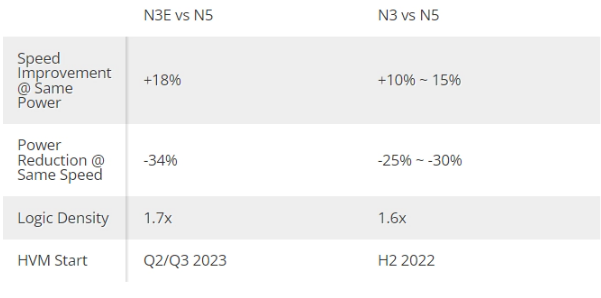

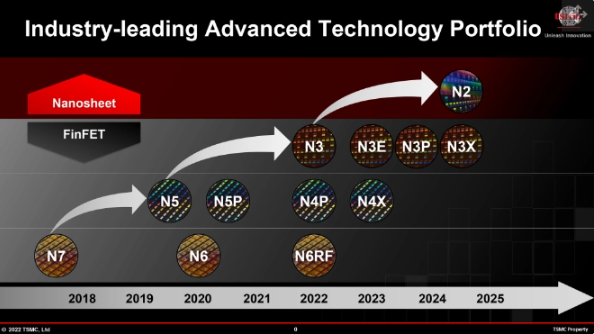

台积电计划在未来两到三年内推出五种 3 纳米级工艺技术,第一代 3nm 工艺 N3 预计将被台积电的大客户苹果用于少数设计,而第二代 3nm 工艺 N3E 将具有改进的工艺窗口,这意味着有更快的产出时间,更高的产量,更高的性能和更低的功耗。

N3E 预计将比 N3 更广泛地被采用,但其大规模生产计划在 2023 年中期或 2023 年第三季度开始,大约在台积电使用其 N3 生产节点启动大批量制造(HVM)一年后。

IT之家了解到,在台积电明年开始 N3E HVM 之后,其计划再提供三个 3 纳米级节点,包括面向性能的 N3P,用于需要高晶体管密度的芯片的 N3S,以及用于性能要求高的应用的 N3X,如微处理器。

相关文章

- Counterpoint:台积电 7/6nm 产能利用率将下滑 10~20%

- 苹果:Apple Music、Apple TV + 和 Apple One 即日起涨价

- 三星电视明年出货目标超 4000 万台,从华星光电、京东方、友达、HKC、LG 显示采购 LCD 面板

- 诺基亚推出 AI 成熟度评估工具:可减少网络拥堵,提高性能

- 消息称 AMD 新一代显卡拥有更大显存:7900 XT 为 20GB,7950 XT 为 24GB

- 谷歌押注人工智能,拟 14 亿元投资一自然语言软件公司

- 英伟达 GeForce NOW 云游戏扩展针对 iPhone / iPad 等触摸优化列表,并新增 8 个游戏

- 欧洲 Ariane 6 火箭推迟至 2023 年底首发,称可与 SpaceX 展开竞争

- 优步 Uber 将成立广告业务部门,以拓展利润来源

- 韩国人工智能芯片公司 Sapeon 计划明年使用台积电 7nm 节点生产新 AI 芯片

- 三星将增加显示驱动 IC、图像传感器外包生产,自有部门增产手机应用处理器等

- vivo 手机将在本月底前支持印度 5G 网络

- 苹果公司削减 iPhone 14 Plus 产量重新评估需求

- 消息称英特尔大幅下调自动驾驶部门 Mobileye 估值至 200 亿美元:远低于预期

- Linus Torvalds 宣布推出首个 Linux Kernel 内核 6.1 RC 预览版:初步支持 Rust 编程语言

- 晶科能源 TOPCon 电池转化效率再创世界纪录,达到 26.1%